好了,进入正是,说说lvds调试。如下图,采用软硬结合板设计,左侧为FPGA主板部分,右侧主要是一些接口,包括Camlink、VGA,中间采用柔性电路板相连。

按照连载3的程序调试lvds接口,使用bank5的差分管脚输出lvds信号,结果采集卡采不到图,这下坏了,开始怀疑引脚分配不正确,一番检查,问题不在这;

接着觉得走线可能不对,看了看PCB,5对差分信号,对内线长差控制在0.254mm内,对间线长差控制在2mm内,走线没有问题;

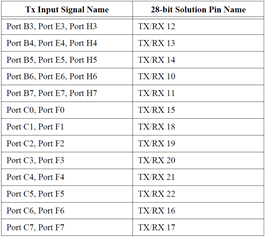

再怀疑Camlink位分配不正确,Camlink在base模式下包含11对差分线(4对数据,1对时钟,2对串口,4对相机控制),Camlink协议中有详细的位分配表,

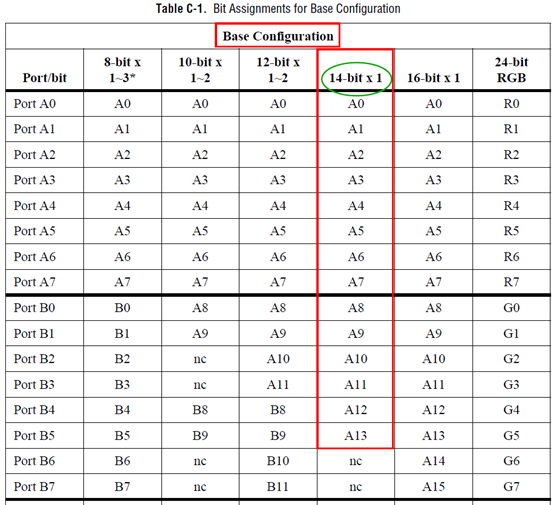

下表说明了在base模式下,各种图像模式(24bit RGB、8bit、10bit、14bit、16bit灰度等)下位分配情况。

查看287手册,就可得到位分配信息。

又是一番检查,位分配完全正确。

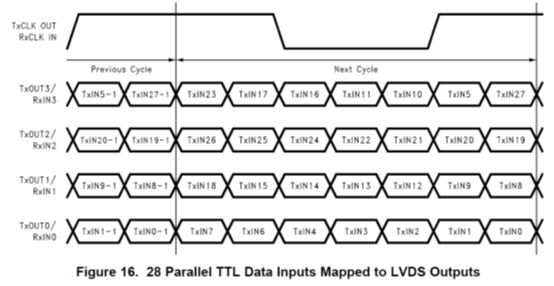

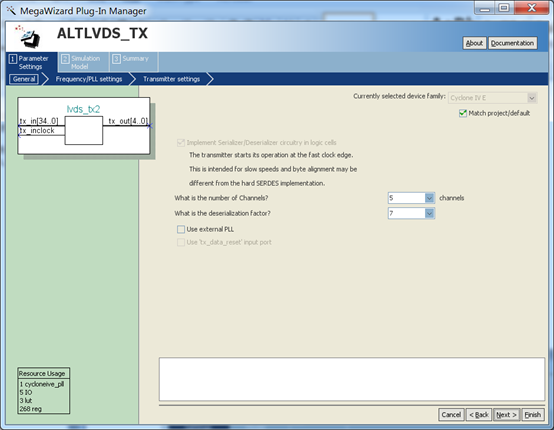

datain3 datain2 datain1 datain0 经过同学的点拨,发现了问题,原来在于时钟的串行化问题,我使用的是lvds_tx核的tx_outclock作为差分时钟,而287的手册上7倍时钟串化对应的时钟信号分别为1,1,0,0,0,1,1,问题已经比较明白了,clk差分通道数据如下,使用5个channels,如下图所示。

cl_clk

重新编译,下载,图像输出正常,lvds调试完成!!

由于lvds_tx核使用了一个ip核,逻辑中使用一个,qsys中使用一个,这样总共4个ip核就用了3个,相关使用外用pll,结果出来的数据又不对了,至今没有解决这个问题,后面有进展了再行吧。