西门子 S7-1200 CPU 1212C AC/DC/继电器 6ES7212-1BE40-0XB0

订货号: 6ES7212-1BE40-0XB0

SIPLUS S7-1200 CPU 1212C 交流/直流/继电器 基于 6ES7212-1BE40-0XB0 带防腐蚀涂层, -40 - +70°C, -25°C 条件下开机, 信号电路板:0, 紧凑型 CPU,AC/DC/继电器, 机载 I/O: 8 DI 24V DC;6 数字输出继电器 2A 2 AI 0-10V DC, 电源: 85-264V AC 47-63Hz 时, 程序存储器/数据存储器 75 KB

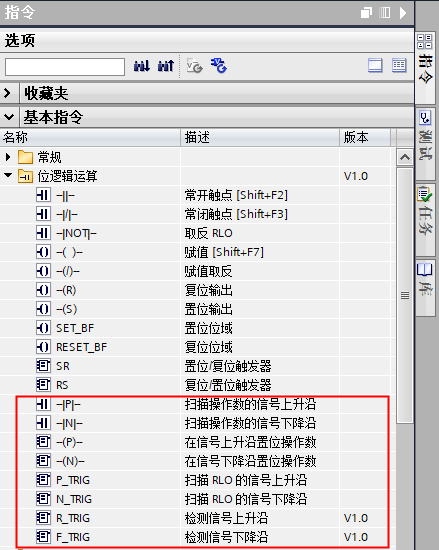

S7-1200 CPU中有多种沿检测指令,这些指令可以用于变量或者逻辑运算结果(RLO)的上升沿、下降沿检测,指令位置如图1所示,指令说明如表1所示。

图1、沿指令位置

| - | 扫描操作数的信号上升沿。 在触点分配的 "IN" 位上检测到正跳变(0->1)时,该触点的状态为 TRUE。该触点逻辑状态随后与能流输入状态组合以设置能流输出状态。P 触点可以放置在程序段中除分支结尾外的任何位置。 指令说明链接 | |

| - | 扫描操作数的信号下降沿。 在触点分配的 "IN" 位上检测到负跳变(1->0)时,该触点的状态为 TRUE。该触点逻辑状态随后与能流输入状态组合以设置能流输出状态。N 触点可以放置在程序段中除分支结尾外的任何位置。 指令说明链接 | |

| - | 在信号上升沿置位操作数。 在进入线圈的能流中检测到正跳变(0->1)时,分配的位 "OUT" 为 TRUE。能流输入状态总是通过线圈后变为能流输出状态。P 线圈可以放置在程序段中的任何位置。 指令说明链接 | |

| - | 在信号下降沿置位操作数。 在进入线圈的能流中检测到负跳变(1->0)时,分配的位 "OUT" 为 TRUE。能流输入状态总是通过线圈后变为能流输出状态。N 线圈可以放置在程序段中的任何位置。 指令说明链接 | |

| - | 扫描 RLO(逻辑运算结果)的信号上升沿。 在 "CLK" 能流输入中检测到正跳变(0->1)时,Q 输出能流或者逻辑状态为 TRUE。 P_TRIG 指令不能放置在程序段的开头或结尾。 指令说明链接 | |

| - | 扫描 RLO(逻辑运算结果)的的信号下降沿。 在 "CLK" 能流输入中检测到负跳变(1->0)时,Q 输出能流或者逻辑状态为 TRUE。 N_TRIG 指令不能放置在程序段的开头或结尾。 指令说明链接 | |

在信号上升沿置位变量。 分配的背景数据块用于存储 CLK 输入的前一状态。在 CLK 能流输入 (LAD) 中检测到正跳变(0->1)时,Q 输出能流或者逻辑状态为 TRUE。在 LAD 中,R_TRIG 指令不能放置在程序段的开头或结尾。 指令说明链接 | ||

在信号下降沿置位变量。 分配的背景数据块用于存储 CLK 输入的前一状态。在 CLK 能流输入 (LAD) 中检测到负跳变(1->0)时,Q 输出能流或者逻辑状态为 TRUE。 在 LAD 中,F_TRIG 指令不能放置在程序段的开头或结尾。 指令说明链接 |

表1、沿指令说明

沿指令使用—|P|—:扫描操作数的信号上升沿使用该指令,可以确定

如果

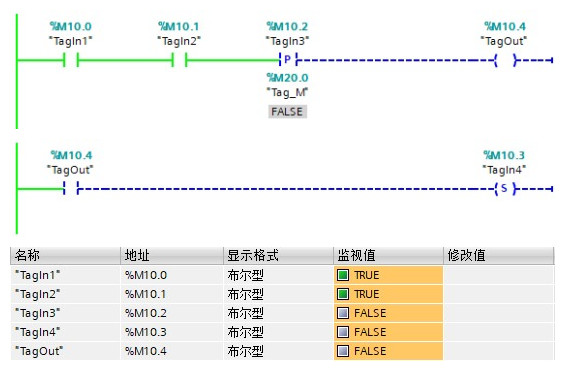

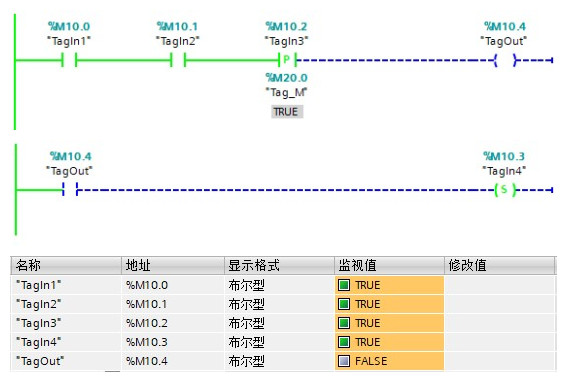

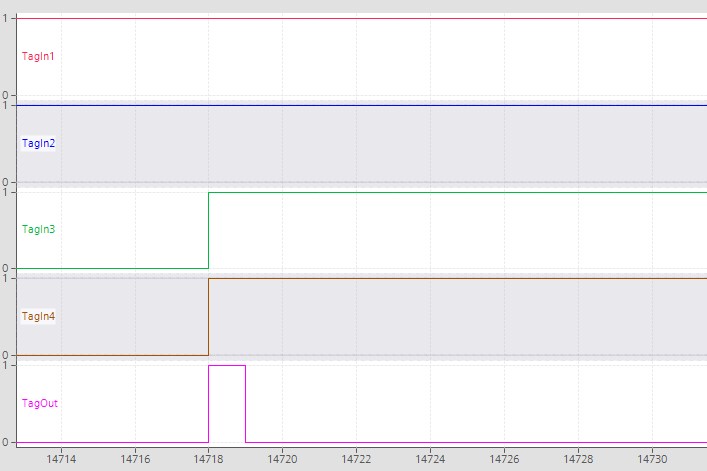

指令参数如表2所示,指令的使用示例如图2-4所示。

| Input | Bool | I、Q、M、D、L或常量 | 要扫描的信号 | |

| InOut | Bool | I、Q、M、D、L | 保存上一次查询的信号状态的边沿存储位 |

表2、扫描操作数的信号上升沿指令参数

图2、扫描操作数的信号上升沿示例

图3、扫描操作数的信号上升沿示例

图4、扫描操作数的信号上升沿示例 Trace 轨迹

在上述示例中,TagIn3为

—|N|—:扫描操作数的信号下降沿使用该指令,可以确定

如果

指令参数如表3所示,指令的使用示例如图5-7所示。

| Input | Bool | I、Q、M、D、L或常量 | 要扫描的信号 | |

| InOut | Bool | I、Q、M、D、L | 保存上一次查询的信号状态的边沿存储位 |

表3、扫描操作数的信号下降沿指令参数

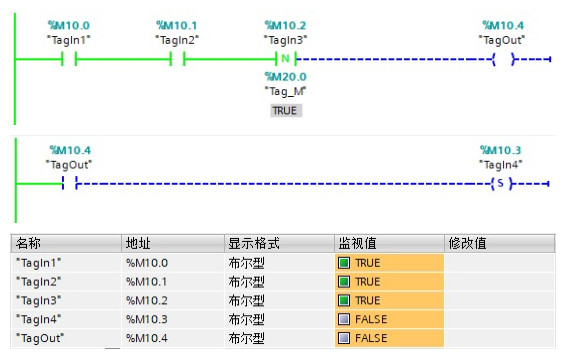

图5、扫描操作数的信号下降沿示例

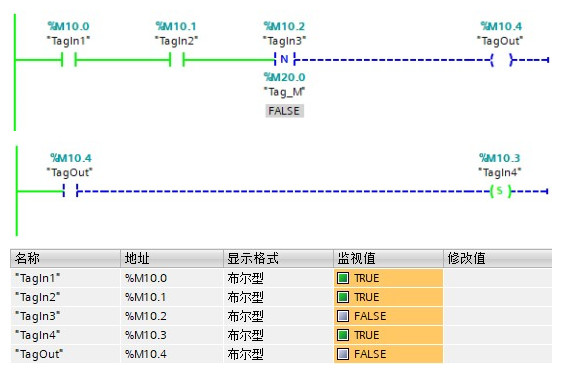

图6、扫描操作数的信号下降沿示例

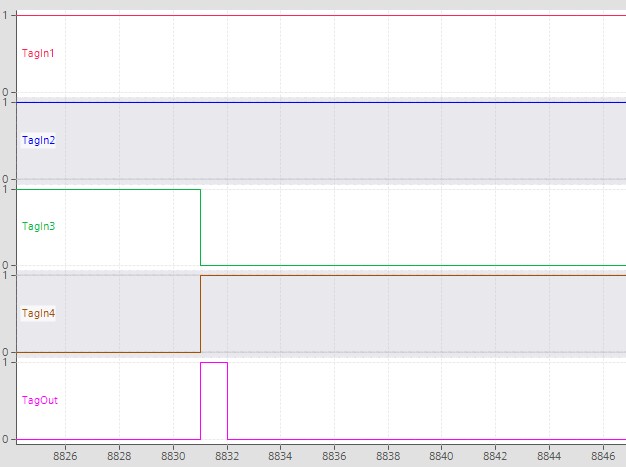

图7、扫描操作数的信号下降沿示例 Trace g轨迹

在上述示例中,TagIn3为

—(P)—:在信号上升沿置位操作数可以使用该指令在逻辑运算结果 (RLO) 从"0"变为"1"时置位

如果上一次扫描的 RLO (

指令参数如表4所示,指令的使用示例如图8-10所示。

| Output | Bool | I、Q、M、D、L | 上升沿置位的操作数 | |

| InOut | Bool | I、Q、M、D、L | 保存上一次查询的信号状态的边沿存储位 |

表4、在信号上升沿置位操作数指令参数

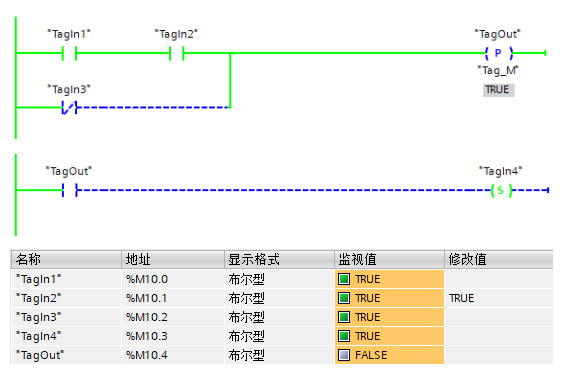

图8、在信号上升沿置为操作数示例

图9、在信号上升沿置为操作数示例

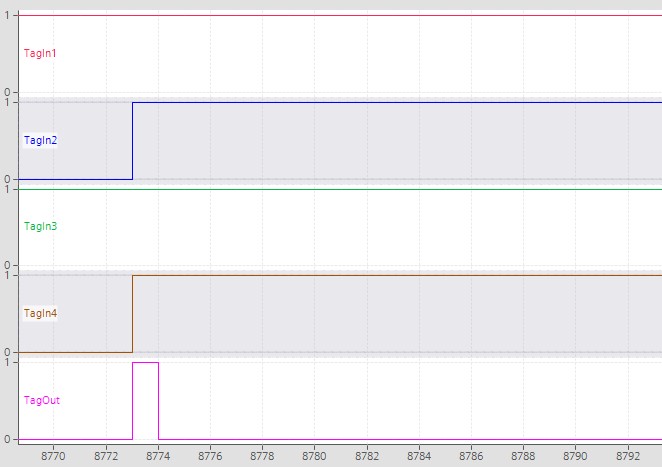

图10、在信号上升沿置为操作数示例 Trace 轨迹

在上述示例中,“TagOut”为

—(N)—:在信号下降沿置位操作数可以使用该指令在逻辑运算结果 (RLO) 从"1"变为"0"时置位

如果上一次扫描的 RLO (

指令参数如表5所示,指令的使用示例如图11-13所示。

| Output | Bool | I、Q、M、D、L | 下降沿置位的操作数 | |

| InOut | Bool | I、Q、M、D、L | 保存上一次查询的信号状态的边沿存储位 |

表5、在信号下降沿置位操作数指令参数

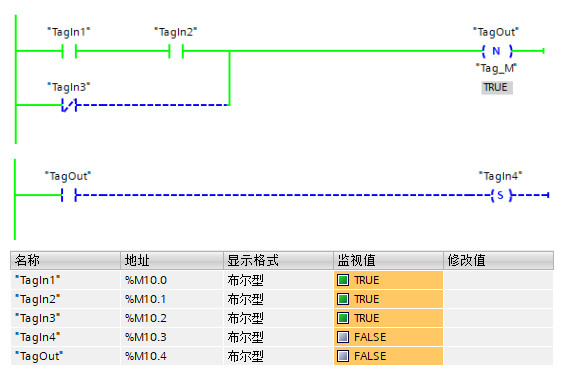

图11、在信号下降沿置为操作数示例

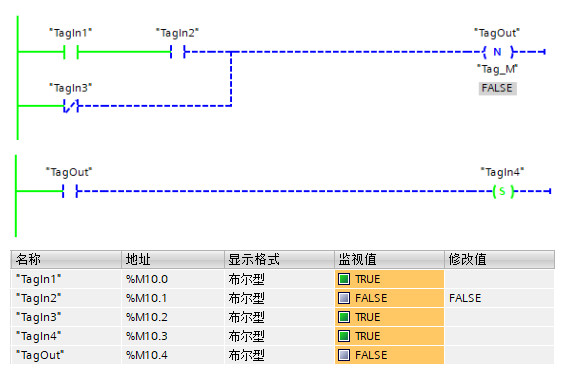

图12、在信号下降沿置为操作数示例

图13、在信号下降沿置为操作数示例 Trace 轨迹

在上述示例中,“TagOut”为

P_TRIG: 扫描 RLO 的信号上升沿![]()

可以使用该指令在 CLK 从"0"变为"1"时置位输出 Q。该指令将比较 CLK 的当前信号状态与 CLK 上一次扫描的信号状态, CLK 上一次扫描的信号状态保存在边沿存储器位

如果上一次扫描的 CLK (

指令参数如表6所示,指令的使用示例如图14-16所示。

| CLK | Input | Bool | I、Q、M、D、L或常量 | 当前逻辑运算结果 (RLO) |

| InOut | Bool | I、Q、M、D、L | 保存上一次查询的信号状态的边沿存储位 | |

| Q | Output | Bool | I、Q、M、D、L | 边沿检测的结果 |

表6、扫描 RLO 的信号上升沿指令参数

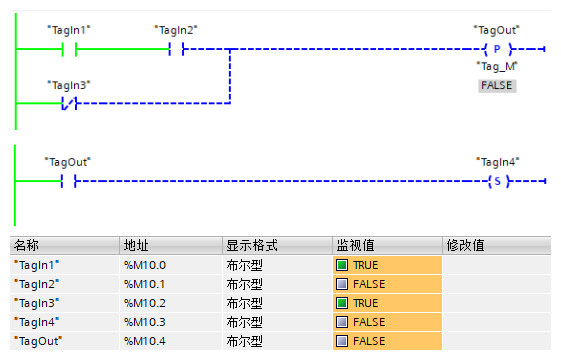

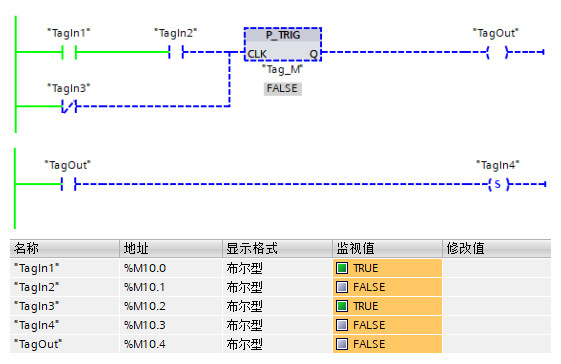

图14、扫描 RLO 的信号上升沿示例

图15、扫描 RLO 的信号上升沿示例

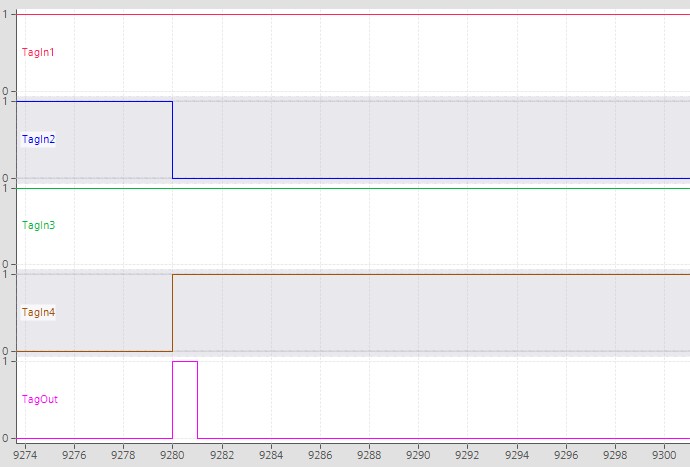

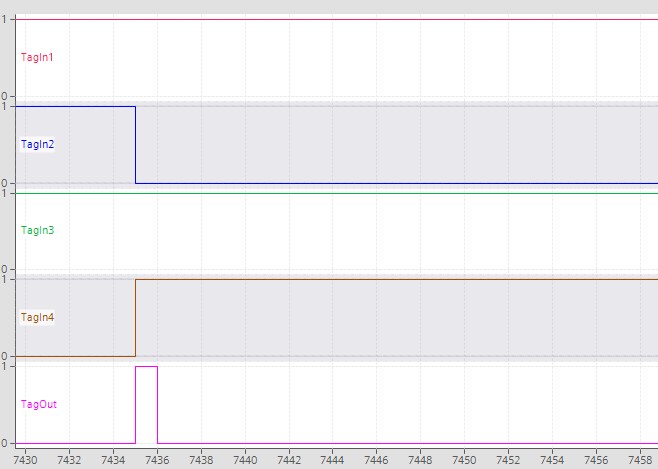

图16、扫描 RLO 的信号上升沿示例 Trace 轨迹

在上述示例中,当操作数“TagIn1”、“TagIn2”、“TagIn3”的逻辑运算结果 (RLO) 即 CLK 输入从“0”变为“1”时,该指令输出 Q 将立即返回状态“1”一个程序周期,此时将操作数“TagOut”置位为一个程序周期,通过“TagOut”将“TagIn4”置位为“1”。

N_TRIG: 扫描 RLO 的信号下降沿![]()

可以使用该指令在 CLK 从"1"变为"0"时置位输出 Q。该指令将比较 CLK 的当前信号状态与 CLK 上一次扫描的信号状态, CLK 上一次扫描的信号状态保存在边沿存储器位

如果上一次扫描的 CLK (

指令参数如表7所示,指令的使用示例如图17-19所示。

| CLK | Input | Bool | I、Q、M、D、L或常量 | 当前逻辑运算结果 (RLO) |

| InOut | Bool | I、Q、M、D、L | 保存上一次查询的信号状态的边沿存储位 | |

| Q | Output | Bool | I、Q、M、D、L | 边沿检测的结果 |

表7、扫描 RLO 的信号下降沿指令参数

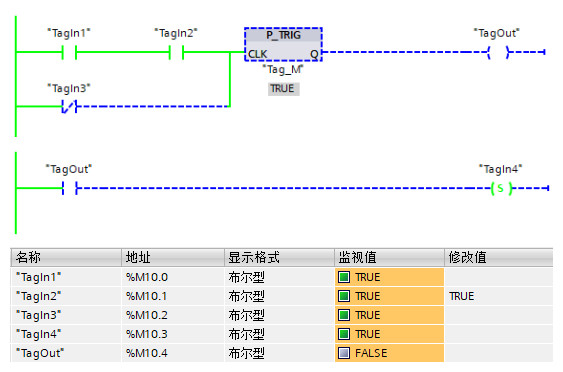

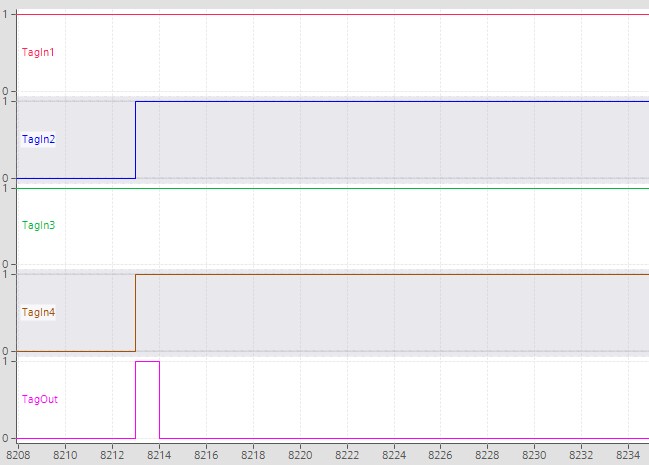

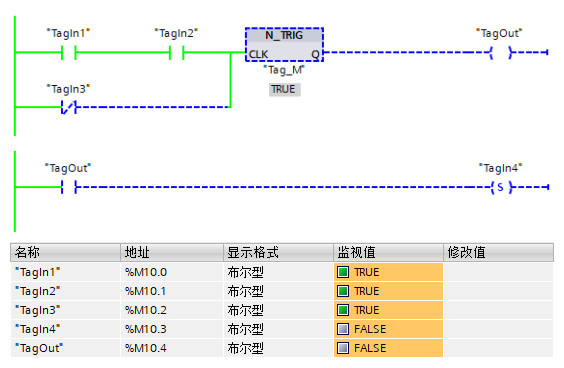

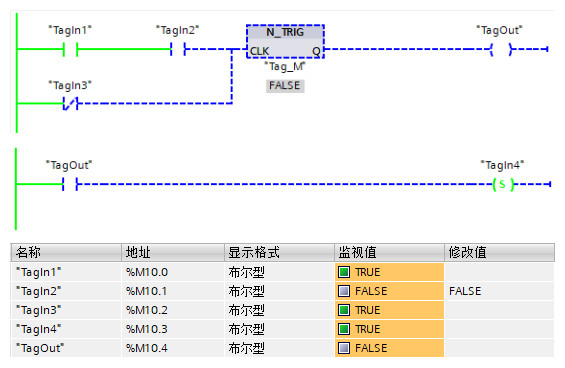

图17、扫描 RLO 的信号下降沿示例

图18、扫描 RLO 的信号下降沿示例

图19、扫描 RLO 的信号下降沿示例 Trace 轨迹

在上述示例中,当操作数“TagIn1”、“TagIn2”、“TagIn3”的逻辑运算结果 (RLO) 即 CLK 输入从“1”变为“0”时,该指令输出 Q 将立即返回状态“1”一个程序周期,此时将操作数“TagOut”置位为一个程序周期,通过“TagOut”将“TagIn4”置位为“1”。

R_TRIG: 检查信号上升沿![]()

可以使用该指令在 CLK 从"0"变为"1"时置位输出 Q。该指令将比较 CLK 的当前信号状态与 CLK 上一次扫描的信号状态, CLK 上一次扫描的信号状态保存在背景数据块中。

如果上一次扫描的 CLK (保存在背景数据块)为“0”,当前 CLK 信号状态为“1”,则说明出现了一个信号上升沿。检测到信号上升沿时,输出 Q 信号状态将在一个程序周期内保持置位为“1”。在其它任何情况下,输出 Q 的信号状态均为“0”。

指令参数如表8所示,指令的使用示例如图20-22所示。

| EN | Input | Bool | I、Q、M、D、L或常量 | 使能输入 |

| ENO | Output | Bool | I、Q、M、D、L | 使能输出 |

| CLK | Input | Bool | I、Q、M、D、L或常量 | 当前逻辑运算结果 (RLO) |

| Q | Output | Bool | I、Q、M、D、L | 边沿检测的结果 |

表8、检查信号上升沿指令参数

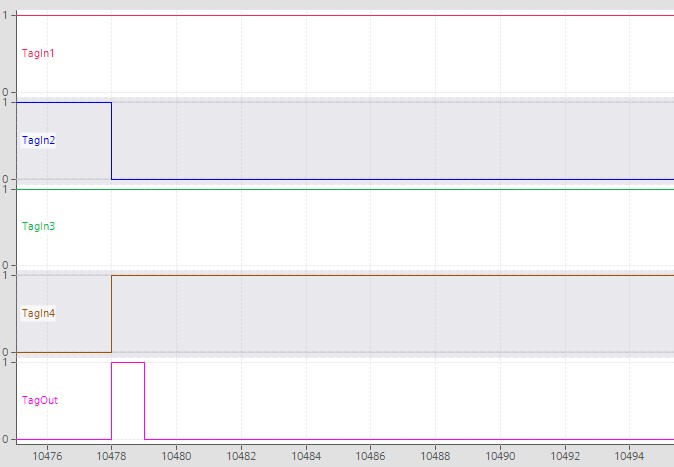

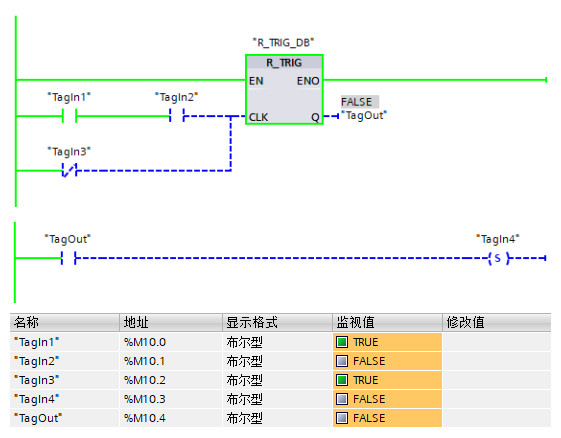

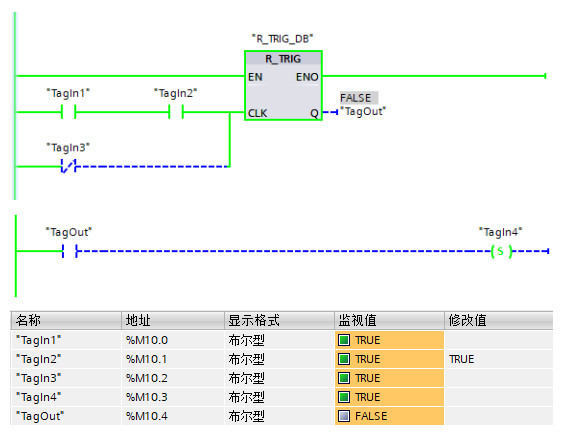

图20、检测信号上升沿示例

图21、检测信号上升沿示例

图22、检测信号上升沿示例 Trace 轨迹

在上述示例中,当操作数“TagIn2”由“0”变为“1”时,当操作数“TagIn1”、“TagIn2”、“TagIn3”的逻辑运算结果 (RLO) 即 CLK 输入从“0”变为“1”时,该指令输出 Q 中生成一个信号上升沿,输出的值将在一个循环周期内为“1“,从图16-3中可以看到此时操作数“TagOut”被置位一个循环周期,通过“TagOut”将“TagIn4”置位为“1”。

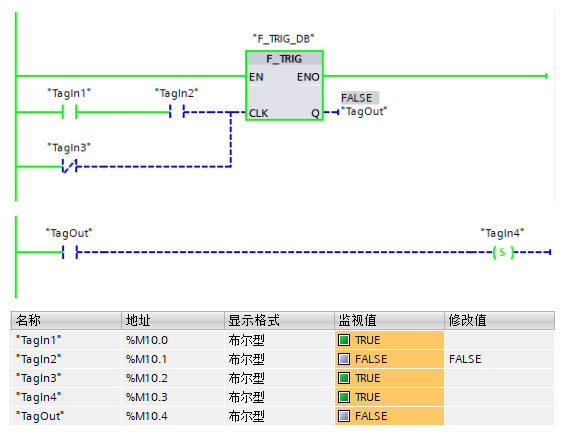

F_TRIG: 检查信号下降沿![]()

可以使用该指令在 CLK 从"1"变为"0"时置位输出 Q。该指令将比较 CLK 的当前信号状态与 CLK 上一次扫描的信号状态, CLK 上一次扫描的信号状态保存在背景数据块中。

如果上一次扫描的 CLK (保存在背景数据块)为“1”,当前 CLK 信号状态为“0”,则说明出现了一个信号下降沿。检测到信号下降沿时,输出 Q 信号状态将在一个程序周期内保持置位为“1”。在其它任何情况下,输出 Q 的信号状态均为“0”。

指令参数如表9所示,指令的使用示例如图23-25所示。

| EN | Input | Bool | I、Q、M、D、L或常量 | 使能输入 |

| ENO | Output | Bool | I、Q、M、D、L | 使能输出 |

| CLK | Input | Bool | I、Q、M、D、L或常量 | 当前逻辑运算结果 (RLO) |

| Q | Output | Bool | I、Q、M、D、L | 边沿检测的结果 |

表9、检查信号下降沿指令参数

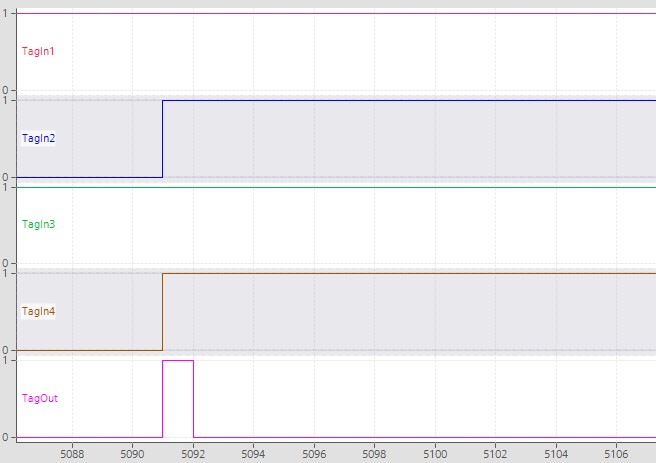

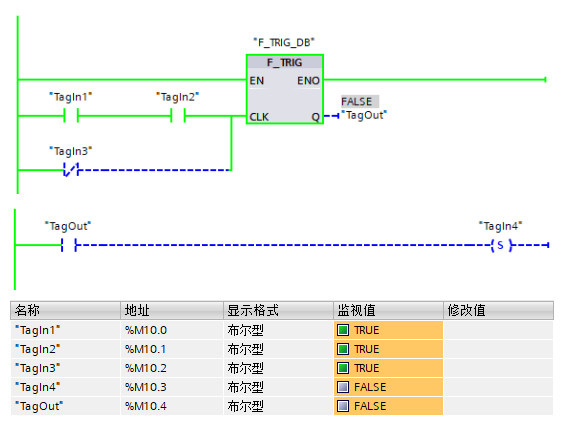

图23、检测信号下降沿示例

图24、检测信号下降沿示例

图25、检测信号下降沿示例 Trace 轨迹

在上述示例中,当操作数“TagIn2”由“1”变为“0”时,操作数“TagIn1”、“TagIn2”、“TagIn3”的逻辑运算结果 (RLO) 即 CLK 输入 从“1”变为“0”,该指令输出 Q 中生成一个信号下降沿,输出的值在一个循环周期内为“1”,从图18-3中可以看到此时操作数“TagOut”被置位一个循环周期,通过“TagOut”将“TagIn4”置位为“1”。

使用注意—|P|—、—|N|—、 —(P)— 、—(N)—、P_TRIG、N_TRIG 均出现边沿存储位,该存储位:

如果使用全局变量( DB 或者 M ),则该全局变量在程序中只能使用一次,一个变量判断多次检测边沿也是一样,每次检测边沿使用不同全局变量。

如果使用局部变量,则只能使用 FC 的 InOut,FB 的 InOut、Static ,不能使用 Temp。并且每个边沿位使用不同的局部变量。

R_TRIG、F_TRIG指令:因为边沿存储位位于背景数据块中,背景数据块、多重背景等不能重复使用,也就是每次使用都是一个新的背景数据块或者多重背景。

常见问题为什么进行边沿检测,得不到正确的输出?

答:边沿检测不能正常输出,原因有以下几种可能:

1、输入必须出现跳变,上升沿是从"0"变为"1",下降沿是从"1"变为"0"

对于—|P|—、—|N|—,检测的是触点上面操作数的输入变化,对于 —(P)— 、—(N)—,检测的是线圈前的逻辑计算结果、对于 P_TRIG、N_TRIG、R_TRIG、F_TRIG 检测是的 CLK 输入。

2、—|P|—、—|N|—、 —(P)— 、—(N)—、P_TRIG、N_TRIG 均出现边沿存储位,该存储位:

3、R_TRIG、F_TRIG指令:背景数据块、多重背景不能重复使用,也就是每次使用都是一个新的背景数据块或者多重背景。

4、边沿输出只有一个扫描周期置位,监视程序是看不到的,需要连接一个置位指令或者加法指令进行捕捉。